メニーコア性能評価用シミュレーション高速化手法

背景

新しいメニーコア開発にはコンピューターによるシミュレーションが欠かせないが、コア数の増加に伴うシミュレーション時間の増加が深刻な問題となっている。

シーズ概要

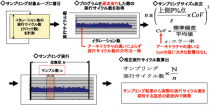

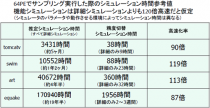

メニーコアにおいて、並列化プログラムを逐次実行し、サンプリング対象ループから、統計的手法を用いて、期待する誤差の範囲内で全実行サイクル数を推定可能なインタレーション数を特定する。そのインタレーション数だけ詳細シミュレーションを行うことにより、少ないシミュレーション時間で高精度の実行サイクル数の推定が可能となる。

応用・展開

シミュレーション時間の短縮によって今までシミュレーションが不可能だったアプリケーションまでも評価可能となる。また当手法はコア数・キャッシュサイズ・キャッシュ最適化の変化に依存しない。

優位性

メニーコア・アーキテクチャ上の並列化プログラム実行に関して、シミュレーションの高速化に成功した例は存在しない。

提供目的

受託研究、共同研究、技術相談

関連論文

- 石塚亮, 大友俊也, 大胡亮太, 木村啓二, 笠原博徳,“プログラム構造に着目したメニーコアアーキテクチャシミュレータの高速化手法”,情報処理学会研究会報告 Vol.2010-ARC-190-20 (SWoPP2010), Aug. 2010.

- 石塚亮, 阿部洋一, 大胡亮太, 木村啓二, 笠原博徳,“科学技術計算プログラムの構造を利用したメニーコアアーキテクチャシミュレーション高速化手法の評価”,情報処理学会研究報告 Vol.2011-ARC-196-14, July. 2011.

掲載日:

2011/09/21