Method for speeding up simulations for assessing many-core performance

2011-0921-02

- researcher's name

-

about researcher KIMURA, Keiji Professor

- affiliation

-

Faculty of Science and Engineering School of Fundamental Science and Engineering

- keyword

-

background

Computer simulations are an integral part to the development of the new many-core processors, but the increase in simulation time as core number is increased is a serious problem.

summary

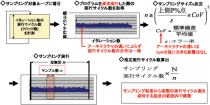

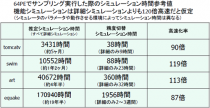

In many-core processors, parallelized programs are executed successively, and from the loops subject to sampling, an estimable interation number for the entire execution cycle is specified within the scope of errors expected based on statistical techniques. By carrying out detailed simulations of only this interation number, it is possible to estimate the execution cycle number with high precision in a short simulation time.

application/development

It is even possible to evaluate applications that until now could not be simulated, thanks to the reduction in simulation time. Moreover, this technique does not rely on changes in core number, cache size or cache optimization.

predominance

There are no examples to date of successes in speeding up the simulation of parallelized program execution on a many-core architecture.

purpose of providing seeds

Sponsord research, Collaboration research, Technical consultation

same researcher's seeds

-

Parallelization of multimedia applications (MPEG2 encoders and decoders) by using the OSCAR compiler

Parallelization of multimedia applications (MPEG2 encoders and decoders) by using the OSCAR compiler

posted:

2014/05/21